# Quadrilateral Current Mode (QCM) Paralleling of Power MOSFETs for Zero-Voltage Switching (ZVS)

Yanfeng Shen, Member, IEEE, Yunlei Jiang, Student Member, IEEE, Hui Zhao, Member, IEEE, Luke Shillaber, Student Member, IEEE, Chaoqiang Jiang, Member, IEEE, and Teng Long, Member, IEEE

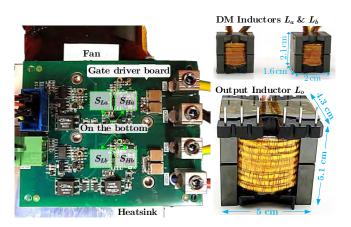

Abstract—This paper proposes a generic zero-voltage switching (ZVS) scheme for parallel power MOSFETs. Uncoupled or inversely-coupled differential-mode (DM) commutation inductors are added to the midpoints (AC terminals) of parallel MOSFET half-bridges (HBs), and a time-delay-based control scheme is applied, generating a circulating current flowing through these commutation inductors. Thus, the inductor currents are reshaped as quadrilaterals, which enable all the parallel transistors to achieve ZVS. The mode of operation of the proposed paralleling technique is entitled quadrilateral current mode (QCM) due to the quadrilateral-shaped commutation inductor currents. The operating principle of the OCM-paralleling technique is detailed mathematically, yielding accurate closed-form analytical expressions for modulation parameters. Finally, simulations and experimental results of a QCM-enabled synchronous Buck dc-dc converter are presented to validate the theoretical considerations.

Index Terms—Parallel power MOSFETs, zero-voltage switching (ZVS), quadrilateral current mode (QCM)

## I. INTRODUCTION

**D** UE to relative low fabrication yields, the current ratings of commercial discrete wide bandgap (WBG) power transistors are limited [1]–[3]. Therefore, it is necessary or even unavoidable to connect multiple WBG power transistors in parallel in high-power applications [3]–[7]. Additionally, the parallel connection of multiple low-current WBG power transistors can be more cost-effective than employing a single high-current transistor [5]–[7].

For the parallel operation of power MOSFETs, the current imbalance caused by MOSFET parameter mismatch and asymmetrical circuit layout [3], [8]–[10] poses a big challenge to efficiency and reliability; therefore, the current imbalance suppression has stimulated much academic and industrial research [6], [7], [9], [11]–[13]. The most direct measure of handling current imbalance is to symmetrize the layout of parallel transistors [10], [14]. However, it is impossible to achieve an absolute symmetrical layout, particularly in highpower-density applications. Employing active gate drivers can dynamically balance the currents flowing through parallel devices [12], [15]; however, these methods require highbandwidth current sensors, and the realization of active gate drives is complicated and costly. By contrast, the passive approaches [6], [7], [11], [16], [17] employ additional magnetic components in parallel branches to suppress the current imbalance; the passive solutions begin prevailing due to their simplicity in implementation and robustness in operation.

In spite of balanced currents achieved with these current sharing schemes, the parallel MOSFETs may suffer uneven thermal stresses due to thermal impedance differences [18], [19]. Multiple devices in parallel significantly reduce the on-state resistance, which in turn lead to a higher parasitic output capacitance and higher switching losses [20]. Thus, for hard-switched power converters employing parallel WBG transistors, the switching loss is predominant at partial loads, and compromises the efficiency performance, particularly at high switching frequencies [21]-[23]. By utilizing the phaseshedding technique [23], [24], the effective number of parallel transistor legs can be adjusted at different loads, which reduces the switching loss at partial loads. In order to lower the partialload switching loss, while simultaneously achieving thermal balance among parallel transistors, a desynchronized control scheme is proposed in [5]; however, only part of the parallel transistors can achieve the zero-voltage switching (ZVS).

For half-bridges (HB) legs, i.e., the basic switch units of classic synchronous Buck/Boost converters and single-/threephase inverters, soft-switching, i.e., zero-voltage switching (ZVS) or zero-current switching (ZCS), can be realized by adding auxiliary resonant circuits to the DC or AC side [25]-[28], or varying the switching frequency to operate in the triangular current mode (TCM) [29]-[34]. The AC auxiliary-resonant-circuits-based soft-switching topologies are also named as the auxiliary resonant commutated pole (ARCP) converters [27], [28]; the main issue is that complex auxiliary switches, inductors, and capacitors are required, particularly for multiphase systems. By contrast, the DC-link auxiliaryresonant-circuit-based soft-switching topologies [25], [26] feature a lower number of auxiliary components; however, the voltage stress of switches is higher than the DC-link voltage, e.g., 1.1-2.5 times, and thus, the loop inductance must be maintained low to avoid high voltage overshoots.

The TCM multiphase interleaving technique [29], [32]– [34] enables all MOSFETs to achieve ZVS for minimized switching loss. This approach, however, requires high-speed zero-current detection, featuring high implementation complexity [31]. Also, the switching frequency varies significantly with the load and output voltage [29], which complicates the electromagnetic interference (EMI) filter design and the digital control [35]. Furthermore, this technique needs relatively large (e.g., greater than several tens of  $\mu$ H in [29], [33], [34]) output inductors, which are typically not desirable in inductive-load

Manuscript received Month xx, 2020; revised Month xx, 2020; accepted Month xx, 2020. (Corresponding author: Teng Long).

The authors are with the Department of Engineering–Electrical Engineering Division, University of Cambridge, Cambridge CB3 0FA, U.K. (e-mail: ys523@cam.ac.uk, yj306@cam.ac.uk, hz352@cam.ac.uk, ls669@cam.ac.uk, cj364@cam.ac.uk, tl322@cam.ac.uk).

applications (e.g., motor drives) due to additional power loss, cost and volume [36], [37].

In order to achieve ZVS for all parallel MOSFETs, this paper proposes a quadrilateral current mode (QCM) modulation scheme. Differential-mode (DM) commutation inductors (ZVS inductors) are added to the midpoints of parallel MOSFET half-bridge (HB) legs, and the QCM modulation scheme enables a circulating current flowing through these DM inductors. This quadrilateral-shaped circulating current helps all the parallel MOSFETs achieve ZVS, resulting in negligible switching loss. The operating principle and mathematical model are detailed, yielding closed-form analytical expressions that directly enable the calculation of the timing parameters needed for ZVS realization. This QCM paralleling technique exhibits much lower switching loss than the conventional direct parallel. In contrast to the TCM multiphase interleaving, this QCM-enabled paralleling technique has the following advantages: 1) the switching frequency can be either fixed or variable; 2) the quadrilateral-shaped DM inductor currents have a negligible impact on the output current; 3) only miniature DM inductors (several  $\mu$ H) are required; 4) in addition to QCM, this paralleling solution is also compatible with the synchronous CCM. The QCM-enabled paralleling technique can be applied to any topologies consisting of basic parallel MOSFET HB units, e.g., the synchronous Buck/Boost dc-dc converters and single-/three-phase inverters.

## II. QUADRILATERAL CURRENT MODE (QCM) PARALLELING SCHEME

## A. Topology

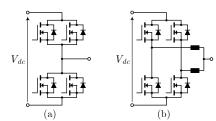

Fig. 1 shows the basic structures of parallel MOSFET HB legs with and without DM commutation inductors. In contrast with the direct parallel showing in Fig. 1(a), the current imbalance caused by the mismatches of transistors and parasitic parameters can be well mitigated by the added DM inductors [5], [37] showing in Fig. 1(b). The DM inductors are typical of much lower inductance than the output filter inductance, and they can be either uncoupled [5] or inversely coupled [37] in implementation.

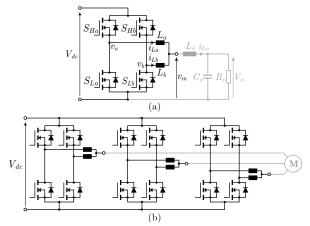

The DM inductor-based paralleling structure can be applied to commonly-used converter topologies, e.g., the synchronous Buck dc-dc converter and the three-phase traction inverter, as shown in Fig. 2. It should be noted that the number of HB legs in parallel is theoretically unlimited. For simplicity, two parallel HB legs with uncoupled inductors are employed in this study.

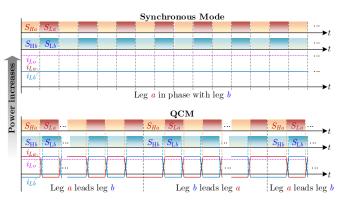

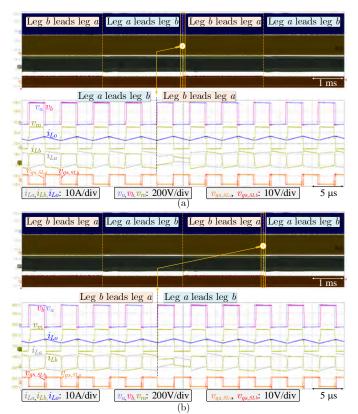

## B. QCM Switching Pattern

A QCM modulation scheme is proposed for the DM commutation inductor-based parallel structure, as shown in Fig. 3. First, the parallel HB legs is divided into two groups: the leading HB leg  $S_{Ha}$ - $S_{La}$  and the lagging leg  $S_{Hb}$ - $S_{Lb}$ , as shown in Fig. 2(a). The gate signals of these parallel legs are desynchronized. Specifically, the turn-off edges between the lagging and leading low-side MOSFETs are delayed by a time of  $\phi_{Loff}$ , whereas the turn-off edges between the highside switches are delayed by a time of  $\phi_{Hoff}$ . With these

Fig. 1. Structures of (a) conventional direct and (b) DM inductor-based parallel power MOSFETs. The DM inductors can be either uncoupled [5] or inversely coupled [37].

Fig. 2. Converter topologies employing the DM inductor-based paralleling structure: (a) synchronous Buck dc-dc converter and (b) three-phase traction inverter.

two turn-off delays of gate signals, the switch-node (midpoint) voltages of the two parallel HB legs are asynchronous, i.e.,  $v_b$  lags behind  $v_a$  by times of  $\delta_{Loff}$  and  $\delta_{Hoff}$  at their rising and falling edges, respectively. The DM commutation inductors  $L_a$  and  $L_b$  are assumed to be identical (i.e.,  $L_a = L_b = L_c$ ) and the commutation inductance  $L_c$  is much lower than the output filter inductance  $L_o$ . Then, the common output voltage of the parallel HB legs,  $v_m$ , can be obtained as

$$v_m(t) = \frac{v_a(t) + v_b(t)}{2}$$

(1)

For the QCM, the common output voltage  $v_m$  has three levels  $(0, +\frac{V_{dc}}{2}, +V_{dc})$  owing to the time delays between  $v_a$ and  $v_b$ , as shown in Fig. 3. Meanwhile, a non-zero voltage difference between  $v_a$  and  $v_b$ , i.e.,  $v_{ab}$ , excites a controllable AC circulating current flowing through the DM commutation inductors  $L_a$  and  $L_b$ :

$$\begin{cases} i_{dm}(t) = \frac{i_{La}(t) - i_{Lb}(t)}{2} \\ 2L_c \frac{\mathrm{d}i_{dm}(t)}{\mathrm{d}t} = v_{ab}(t) \end{cases}$$

(2)

The amplitude of the circulating current  $i_{dm}$  is mainly determined by the volt-second product of  $v_{ab}$  during the time delays  $\delta_{Loff}$  and  $\delta_{Hoff}$ , as shown in Fig. 3. The two time delays  $\delta_{Loff}$  and  $\delta_{Hoff}$  also represent the positive and negative pulse widths of  $v_{ab}$ . That is, the circulating current  $i_{dm}$  is regulated by controlling the pulse widths of  $v_{ab}$ .

The output current  $i_{Lo}$  is determined by the common output voltage  $v_m$ , the output voltage  $v_o$  and the filter inductance  $L_o$ , i.e.,

$$L_o \frac{\mathrm{d}i_{Lo}(t)}{\mathrm{d}t} = v_m(t) - V_o \tag{3}$$

Fig. 3. Typical operating waveforms of the QCM-paralleled power MOSFET half-bridges (see Fig. 2(a)). The deadtimes between high- and low-side switches are denoted as  $\sigma_{LHa}$  and  $\sigma_{LHb}$  for leg  $S_{Ha}$ - $S_{La}$ , and  $\sigma_{LHb}$  and  $\sigma_{HLb}$  for leg  $S_{Hb}$ - $S_{Lb}$ . The turn-off time delays between low-side switches and between high-side switches are denoted as  $\phi_{Loff}$  and  $\phi_{Hoff}$ , respectively. The switch-node (midpoint) voltage  $v_b$  lags behind  $v_a$  by  $\delta_{Loff}$  and  $\delta_{Hoff}$  and  $\delta_{Hoff}$  and fall edges; the two time delays  $\delta_{Loff}$  and  $\delta_{Hoff}$  also represent the positive and negative pulse widths of voltage  $v_{ab}$ .

According to Kirchhoff's circuit law, the output current can be obtained from the two inductor currents as

$$i_{Lo}(t) = i_{La}(t) + i_{Lb}(t)$$

(4)

From (2) and (4), the two inductor currents  $i_{La}$  and  $i_{Lb}$  can be expressed by the circulating and output currents, i.e.,

$$\begin{cases} i_{La}(t) = \frac{i_{Lo}(t)}{2} + i_{dm}(t) \\ i_{Lb}(t) = \frac{i_{Lo}(t)}{2} - i_{dm}(t) \end{cases}$$

(5)

As seen from (5) and Fig. 3, the two inductor currents  $i_{La}$  and  $i_{Lb}$  are shaped by both the output current  $i_{Lo}$  and the circulating current  $i_{dm}$ . Increasing the amplitude of  $i_{dm}$  enables  $i_{La}$  and  $i_{Lb}$  to reach a negative boundary before the corresponding high-side MOSFETs  $S_{Ha}$  and  $S_{Hb}$  are turned ON. That is, the body diodes of  $S_{Ha}$  and  $S_{Hb}$  conduct first before their gates are applied with a forward bias voltage, leading to ZVS-ON for  $S_{Ha}$  and  $S_{Lb}$  can also achieve the ZVS-ON due to the sufficiently positive inductor currents  $i_{La}$  and  $i_{Lb}$  before their gate turn-on signals are applied. Hence, by

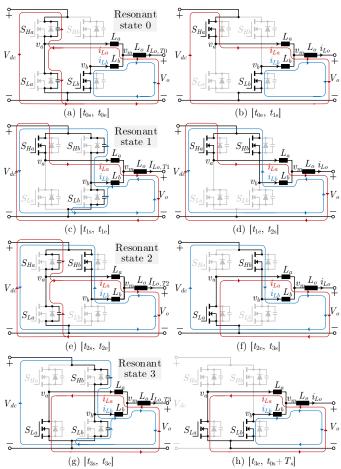

Fig. 4. Operating states of QCM-paralleled MOSFET HBs (configured as a synchronous Buck dc-dc converter, see Fig. 2(a)) within a full switching cycle  $[t_{0s}, t_{0s} + T_s]$ . The four resonant stages, (a), (c), (c) and (g), are termed as resonant states 0, 1, 2, and 3, respectively.

controlling the pulse widths ( $\delta_{Loff}$  and  $\delta_{Hoff}$ ) of  $v_{ab}$ , all the parallel MOSFETs are able to achieve the ZVS for minimized switching loss. The commutation inductor currents  $i_{La}$  and  $i_{Lb}$  exhibit quadrilateral shapes, and therefore, the mode of operation is termed as quadrilateral current mode (QCM).

## C. Operating Principle

The synchronous Buck dc-dc converter (see Fig. 2(a)) is taken as an application example to illustrate the operating principle of the proposed QCM paralleling scheme.

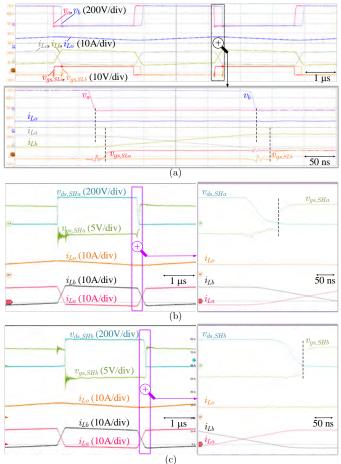

Typical operating waveforms of QCM are shown in Fig. 3 where four resonant stages, (a), (c), (c) and (g), occur during intervals  $T_0$ ,  $T_1$ ,  $T_2$ , and  $T_3$ , respectively. For each resonant state interval, subscript 's' denotes the starting instant and 'e' denotes the ending instant, e.g.,  $t_{0s}$  and  $t_{0e}$  represent the starting and ending instants of interval  $T_0$  (resonant stage (a)), respectively. Four non-resonant stages are termed as (b), (d), (f) and (h) in Fig. 3. Therefore, there are total eight stages within one switching cycle  $[t_{0s}, t_{0s} + T_s]$  where  $T_s$  denotes the switching period. The equivalent circuits and current loops of these operating stages are shown in Fig. 4.

• Non-resonant Stages:

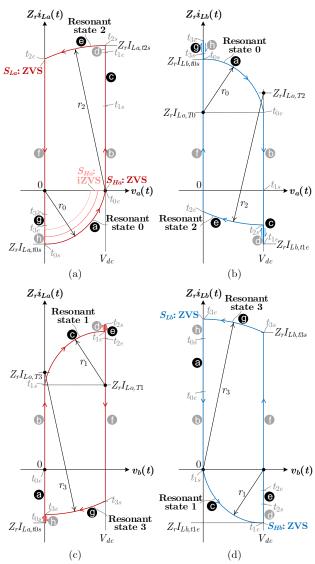

Fig. 5. State-plane diagram of the scaled inductor currents with respect to the switch-node voltages for the QCM-paralleled power MOSFET HBs (see Fig. 2(a)). (a)  $Z_r i_{La}(t)$  with respect to  $v_a(t)$ . (b)  $Z_r i_{Lb}(t)$  with respect to  $v_a(t)$ . (c)  $Z_r i_{La}(t)$  with respect to  $v_b(t)$ . (d)  $Z_r i_{Lb}(t)$  with respect to  $v_b(t)$ .

In operating stages (b), (d), (f), and (h), the MOSFETs are fully turned ON or OFF, operating in the ohmic region with a channel resistance of  $R_{ds,on}$  or in the cut-off region with an almost infinite channel resistance. In these stages, the switchnode (midpoint) voltages of the parallel legs,  $v_a$  and  $v_b$ , are given as

$$\begin{cases} v_{a}(t) = s_{a}(t)V_{dc} - i_{La}(t)R_{ds,on} \\ v_{b}(t) = s_{b}(t)V_{dc} - i_{Lb}(t)R_{ds,on} \end{cases}$$

(6)

in which the bi-logic variables  $s_a(t)$  and  $s_b(t)$  equal to 1 and 0 when the corresponding high- and low-side MOSFETs are turned ON, respectively. In these non-resonant stages, the operation follows the differential equations in (2) and (3).

## • Resonant Stages:

Operating stages (a), (c), (e), and (g) represent the resonant states formed by the parasitic output capacitances of MOS-FETs, the DM inductors ( $L_a$  and  $L_b$ ) and the output inductor

$L_o$ . Resonant states 0 and 2 in stages (a) and (c) have the same characteristic impedance as shown in Figs. 4(a) and (e), while resonant states 1 and 3 in stages (c) and (g) have the same characteristic impedance as shown in Figs. 4(c) and (g). These characteristic impedances are obtained as

$$Z_r = \begin{cases} \sqrt{\frac{L_a + L_b || L_o}{C_{oss,SHa} + C_{oss,SLa}}}, & \text{Resonant states 0 and 2} \\ \sqrt{\frac{L_b + L_a || L_o}{C_{oss,SHb} + C_{oss,SLb}}}, & \text{Resonant states 1 and 3} \end{cases}$$

(7)

where  $C_{oss,SHa}$ ,  $C_{oss,SLa}$ ,  $C_{oss,SHb}$  and  $C_{oss,SLb}$  represent the parasitic output capacitances of  $S_{Ha}$ ,  $S_{La}$ ,  $S_{Hb}$  and  $S_{Lb}$ , respectively. Assuming these parasitic capacitances are equal to  $C_{o,qe}$ , the characteristic impedance and the resonant angular frequency can be expressed as

$$Z_r = \sqrt{\frac{L_c + L_c || L_o}{2C_{o,qe}}} \tag{8}$$

$$\omega_r = \frac{1}{\sqrt{2C_{o,qe}(L_c + L_c || L_o)}} \tag{9}$$

where the charge-equivalent capacitance  $C_{o,qe}$  is a fixed capacitance that gives the same stored charge as a nonlinear parasitic output capacitor  $C_{oss}$  while the drain-source voltage  $v_{ds}$  is rising from 0 to  $V_{dc}$ , i.e.,

$$C_{o,qe} = \frac{Q_{oss}}{V_{dc}} = \frac{1}{V_{dc}} \int_0^{V_{dc}} C_{oss} \mathrm{d}v_{ds}$$

(10)

where  $Q_{oss}$  represents the charge stored in the parasitic output capacitor of a transistor at a drain-source voltage of  $V_{dc}$ .

Considering  $L_c \ll L_o$ , the output inductor  $L_o$  can be regarded as a constant current source during the short resonant transitions, i.e., in stages (a), (c), (e), and (g); the output currents in the four resonant stages are represented by  $I_{Lo,T0}$ ,  $I_{Lo,T1}$ ,  $I_{Lo,T2}$ , and  $I_{Lo,T3}$ , respectively. The characteristic impedance and the resonant angular frequency in (8) and (9) can be further simplified as

$$Z_r = \sqrt{\frac{L_c}{C_{o,qe}}} \tag{11}$$

$$\omega_r = \frac{1}{2\sqrt{L_c C_{o,qe}}} \tag{12}$$

#### • Analysis of Operation:

۷

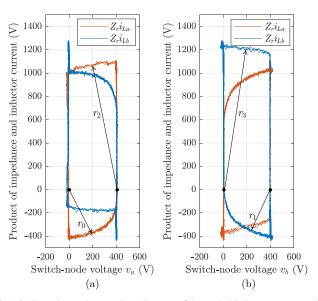

The state-plane diagram [31], [35], [38] depicting the trajectory of inductor current (scaled by the characteristic impedance of the resonant circuit) with respect to the switch-node voltage, is a useful representation for the analysis of the QCM-based ZVS operation, as illustrated in Fig. 5.

Stage (a) (Resonant State 0)  $[t_{0s}, t_{0e}]$ : Before  $t_{0s}$ , the two low-side switches  $S_{La}$  and  $S_{Lb}$  are conducting but with different directions of current flows, as shown in Figs. 3 and 4(h). At  $t_{0s}$ ,  $S_{La}$  is turned OFF, and then the output capacitances  $C_{oss,SLa}$  and  $C_{oss,SHa}$  begin to resonate with  $L_a$ ,  $L_b$  and  $L_o$ , as shown in Figs. 3 and 4(a). The resonant transition is described in the state-plane diagrams (Figs. 5(a), and 5(b)). The resonant circle of  $Z_r i_{La}(t)$  versus  $v_a(t)$  is centered at (0, 0) and starting from (0,  $Z_r I_{La,t0s})$  as the initial

condition. The time elapsed between two points on the circular trajectory is propositional to the angle subtended at the center [38]. Likewise, the resonant circle of  $Z_r i_{Lb}(t)$  versus  $v_a(t)$  is centered at  $(0, Z_r I_{Lo,T0})$  and starting from  $(0, Z_r I_{Lb,t0s})$ . The radii of the two circles  $Z_r i_{La}(t)$  versus  $v_a(t)$  and  $Z_r i_{Lb}(t)$  versus  $v_a(t)$  are identical and termed as  $r_0$ . The resonant voltage and current transitions can be described with

$$\begin{cases} i_{La}(t) = I_{La,t0s} \cos[\omega_r(t - t_{0s})] \\ i_{Lb}(t) = I_{Lo,T0} - I_{La,t0s} \cos[\omega_r(t - t_{0s})] \\ v_a(t) = -Z_r I_{La,t0s} \sin[\omega_r(t - t_{0s})] \\ v_b(t) = 0 \end{cases}$$

(13)

where  $I_{La,t0s}$  denotes the current of  $i_{La}$  at  $t = t_{0s}$ . The circle radius in Fig. 5(a) can be obtained as

$$r_0 = Z_r |I_{La,t0s}| \tag{14}$$

If the radius is not less than  $V_{dc}$ , i.e.,  $r_0 \ge V_{dc}$ , then the switch-node voltage  $v_a$  can rise to the dc-bus voltage  $V_{dc}$ , implying  $C_{oss,SHa}$  is discharged to 0 V at  $t = t_{0e}$ , after which  $S_{Ha}$  can be turned ON under ZVS. Otherwise, the resonant trajectories will follow the dashed lines in Fig. 5(a), and  $v_a$ cannot reach  $V_{dc}$  before  $Z_r i_{La}$  becomes positive, resulting in incomplete ZVS (iZVS) [39] for  $S_{Ha}$ . The minimum  $I_{La,t0s}$ allowing for full ZVS is termed as the valley inductor current  $I_{Lx,vl}$ , and it can be obtained as

$$r_{0} \geq V_{dc}$$

$$\Rightarrow -I_{La,t0s} \geq \frac{V_{dc}}{Z_{r}} = V_{dc} \sqrt{\frac{C_{o,ge}}{L_{c}}} = \sqrt{\frac{V_{dc}Q_{oss}}{L_{c}}} = -I_{Lx,vl}$$

(15)

The valley current  $I_{Lx,vl}$  is negative and it is independent on the duty cycle and the output voltage, which is different from the TCM scheme.

Stage (b)  $[t_{0e}, t_{1s}]$ : At  $t_{0e}$ , the high-side switch  $S_{Ha}$  of the leading leg is turned ON under ZVS whereas the low-side switch  $S_{Lb}$  of the lagging leg is still freewheeling. Compared with the dc-bus voltage, the voltage drops over  $S_{Ha}$  and  $S_{Lb}$  can be neglected. Thus, the switch-node (midpoint) voltage difference,  $v_{ab}$ , equals the dc-bus voltage  $V_{dc}$ , causing the inductor current  $i_{La}$  to rise linearly and  $i_{Lb}$  to fall linearly, i.e.,

$$\begin{cases} i_{La}(t) = \left(\frac{1-2D}{4L_o} + \frac{1}{2L_c}\right) V_{dc}(t - t_{0e}) \\ i_{Lb}(t) = I_{Lb,t0e} + \left(\frac{1-2D}{4L_o} - \frac{1}{2L_c}\right) V_{dc}(t - t_{0e}) \\ v_{ab} = V_{dc} - R_{ds,on}(i_{La} - i_{Lb}) \approx V_{dc} \end{cases}$$

(16)

where  $I_{Lb,t0e}$  is the current of  $L_b$  at  $t = t_{0e}$ .

Stage  $\bigcirc$  (Resonant State 1)  $[t_{1s}, t_{1e}]$ : The low-side switch of the lagging leg,  $S_{Lb}$ , can be turned OFF before  $i_{Lb}$  falls to 0. For simplicity of analysis, it is considered to turn OFF  $S_{Lb}$ at  $t_{1s}$  when the inductor current  $i_{Lb} = 0$ . Since both switches of the lagging leg are turned OFF, their output capacitances appear and begin to resonate with the inductors. The resonant transitions are described with two circles in Figs. 5(c) and (d). The circle centers for  $Z_r i_{La}(t)$  versus  $v_b(t)$  and  $Z_r i_{Lb}(t)$ versus  $v_b(t)$  are located at  $(V_{dc}, Z_r I_{Lo,T1})$  and  $(V_{dc}, 0)$ , respectively. The resonant voltage and current transitions can be described with

$$\begin{cases} i_{La}(t) = I_{Lo,T1} + \frac{V_{dc}}{Z_r} \sin[\omega_r(t - t_{1s})] \\ i_{Lb}(t) = -\frac{V_{dc}}{Z_r} \sin[\omega_r(t - t_{1s})] \\ v_a(t) = V_{dc} \\ v_b(t) = V_{dc} - V_{dc} \cos[\omega_r(t - t_{1s})] \end{cases}$$

(17)

The switch-node voltage  $v_b$  reaches  $V_{dc}$  at  $t_{1e}$ , indicating the parasitic output capacitance  $C_{oss,SHb}$  is discharged to 0. The switch  $S_{Hb}$  can be subsequently turned ON under ZVS. As observed in Fig. 5(d), the inductor current  $i_{Lb}$  falls to its minimum at  $t_{1e}$ , reaching  $I_{Lb,t1e}$ . The circle radius in Fig. 5(d),  $r_1$ , is obtained as

$$r_1 = V_{dc} = Z_r |I_{Lb,t1e}|$$

(18)

From (18), we have

$$I_{Lb,t1e} = -\frac{V_{dc}}{Z_r} = I_{Lx,vl} \tag{19}$$

It means that the valley current of  $i_{Lb}$  is identical to the valley of  $i_{La}$ .

Stage (1)  $[t_{1e}, t_{2s}]$ : The switch  $S_{Hb}$  is turned ON under ZVS at  $t_{1e}$ . Thus, both high-side switches,  $S_{Ha}$  and  $S_{Hb}$ , are ON, but are carrying different currents in opposite directions, as shown in Fig. 4(d). Solving the differential equations (2) and (3) yields

$$\begin{pmatrix}

i_{La}(t) = \left(\frac{I_{Lo,T1}}{2} - \frac{(1-D)V_{dc}}{R_{ds,on}}\right) \exp\left(-\frac{R_{ds,on}}{2L_o}(t-t_{1e})\right) \\

+I_{dm,t1e} \exp\left(-\frac{R_{ds,on}}{L_c}(t-t_{1e})\right) + \frac{(1-D)V_{dc}}{R_{ds,on}} \\

i_{Lb}(t) = \left(\frac{I_{Lo,T1}}{2} - \frac{(1-D)V_{dc}}{R_{ds,on}}\right) \exp\left(-\frac{R_{ds,on}}{2L_o}(t-t_{1e})\right) \\

-I_{dm,t1e} \exp\left(-\frac{R_{ds,on}}{L_c}(t-t_{1e})\right) + \frac{(1-D)V_{dc}}{R_{ds,on}} \\

v_{ab} = -R_{ds,on}[i_{La}(t) - i_{Lb}(t)]$$

(20)

where  $I_{dm,t1e} = \frac{I_{La,t1e} - I_{Lb,t1e}}{2}$  with  $I_{La,t1e}$  and  $I_{Lb,t1e}$  representing the currents of  $L_a$  and  $L_b$  at  $t = t_{1e}$ . This stage terminates at  $t = t_{2s}$  when  $S_{Ha}$  is turned OFF.

Stage (c) (Resonant State 2)  $[t_{2s}, t_{2e}]$ : After  $S_{Ha}$  is turned OFF, the parasitic output capacitances of  $S_{Ha}$  and  $S_{La}$  start to resonate with  $L_a$  and  $L_b$ , as shown in Figs. 4(e), 5(a) and 5(b). The switch-node voltage  $v_a$  is falling, and the two inductor currents  $i_{La}$  and  $i_{Lb}$  are decreasing and increasing, respectively. The resonant trajectories are minor arcs of two circles with centers located at  $(V_{dc}, 0)$  and  $(V_{dc}, Z_r I_{Lo,T2})$ , respectively. The equations describing the resonant transitions are obtained as

$$\begin{cases} i_{La}(t) = I_{La,t2s} \cos[\omega_r(t-t_{2s})] \\ i_{Lb}(t) = I_{Lo,T2} - I_{La,t2s} \cos[\omega_r(t-t_{2s})] \\ v_a(t) = V_{dc} - Z_r I_{La,t2s} \sin[\omega_r(t-t_{2s})] \\ v_b(t) = V_{dc} \end{cases}$$

(21)

where  $I_{La,t2s}$  denotes the current of  $L_a$  at  $t_{2s}$ . The radius of the arcs is directly derived as

$$r_2 = Z_r I_{La,t2s} \tag{22}$$

The switch-node voltage  $v_a$  drops to 0 at  $t_{2e}$  after which  $S_{La}$  can be turned ON under ZVS.

IEEE TRANSACTIONS ON POWER ELECTRONICS REGULAR PAPER

Stage (f)  $[t_{2e}, t_{3s}]$ : After  $t_{2e}$ , the low-side switch of the leading leg,  $S_{La}$ , conducts reversely, whereas the high-side switch of the lagging leg,  $S_{Hb}$ , remains ON. As with stage (b), the voltage drops over  $S_{La}$  and  $S_{Hb}$  are far lower than the dc-bus voltage  $V_{dc}$ , and therefore can be neglected. The inductor currents can be described as

$$\begin{cases} i_{La}(t) = I_{La,t2e} + \left(\frac{1-2D}{4L_o} - \frac{1}{2L_c}\right) V_{dc}(t - t_{2e}) \\ i_{Lb}(t) = I_{Lb,t2e} + \left(\frac{1-2D}{4L_o} + \frac{1}{2L_c}\right) V_{dc}(t - t_{2e}) \\ v_{ab} = -V_{dc} - R_{ds,on}[i_{La}(t) - i_{Lb}(t)] \approx -V_{dc} \end{cases}$$

(23)

where  $I_{La,t2e}$  and  $I_{Lb,t2e}$  are the currents of  $L_a$  and  $L_b$  at  $t = t_{2e}$ , respectively. This stage ends with  $S_{Hb}$  being turned OFF at  $t_{3s}$ .

Stage (2) (Resonant State 3)  $[t_{3s}, t_{3e}]$ : As  $S_{Hb}$  turns OFF, the parasitic output capacitances of  $S_{Hb}$  and  $S_{Lb}$  begin to resonate with  $L_a$  and  $L_b$ , causing  $C_{oss,SHb}$  and  $C_{oss,SLb}$  to be charged and discharged, respectively. The resonant trajectories are represented by the minor arcs in Figs. 5(c) and (d). The centers of these minor arcs are located at  $(0, Z_r I_{Lo,T3})$  for  $Z_r i_{La}(t)$  versus  $v_b(t)$  and (0, 0) for  $Z_r i_{Lb}(t)$  versus  $v_b(t)$ . The mathematical expressions of the resonant transitions are given as

$$\begin{cases} i_{La}(t) = I_{Lo,T3} - I_{Lb,t3s} \cos[\omega_r(t - t_{3s})] \\ -\frac{V_{dc}}{Z_r} \sin[\omega_r(t - t_{3s})] \\ i_{Lb}(t) = I_{Lb,t3s} \cos[\omega_r(t - t_{3s})] + \frac{V_{dc}}{Z_r} \sin[\omega_r(t - t_{3s})] \\ v_a(t) = 0 \\ v_b(t) = V_{dc} \cos[\omega_r(t - t_{3s})] - Z_r I_{Lb,t3s} \sin[\omega_r(t - t_{3s})] \end{cases}$$

(24)

where  $I_{Lb,t3s}$  denotes the current of  $L_b$  at  $t = t_{3s}$ . The radius of the two circle arcs can be obtained as

$$r_3 = \sqrt{\left(Z_r I_{Lb,t3s}\right)^2 + V_{dc}^2} = Z_r I_{Lb,t3e}$$

(25)

where  $I_{Lb,t3e}$  denotes the current of  $L_b$  at  $t = t_{3e}$ . The resonance terminates at  $t = t_{3e}$  when  $v_b$  falls to 0 and the body diode of  $S_{Lb}$  starts to conduct. Subsequently,  $S_{Lb}$  can achieve the ZVS-ON.

Stage (h)  $[t_{3e}, t_{0s} + T_s]$ : The two low-side MOSFETs  $S_{La}$  and  $S_{Lb}$  are fully turned on, operating in the ohmic region. Thus, the two switch-node voltages  $v_a$  and  $v_b$  are determined by the channel resistances and currents of  $S_{La}$  and  $S_{Lb}$ . Solving the differential equations (2) and (3) yields the mathematical expressions of voltages and currents:

$$\begin{cases} i_{La}(t) = \left(\frac{I_{Lo,T3}}{2} + \frac{DV_{dc}}{R_{ds,on}}\right) \exp\left(-\frac{R_{ds,on}}{2L_o}(t-t_{3e})\right) \\ +I_{dm,t3e} \exp\left(-\frac{R_{ds,on}}{L_c}(t-t_{3e})\right) - \frac{DV_{dc}}{R_{ds,on}} \\ i_{Lb}(t) = \left(\frac{I_{Lo,T3}}{2} + \frac{DV_{dc}}{R_{ds,on}}\right) \exp\left(-\frac{R_{ds,on}}{2L_o}(t-t_{3e})\right) \\ -I_{dm,t3e} \exp\left(-\frac{R_{ds,on}}{L_c}(t-t_{3e})\right) - \frac{DV_{dc}}{R_{ds,on}} \\ v_{ab} = -R_{ds,on}[i_{La}(t) - i_{Lb}(t)] \end{cases}$$

(26)

where  $I_{dm,t3e} = \frac{I_{La,t3e} - I_{Lb,t3e}}{2}$  with  $I_{La,t3e}$  and  $I_{Lb,t3e}$  being the currents of  $L_a$  and  $L_b$  at  $t = t_{3e}$ . This stage terminates at  $t = t_{0s} + T_s$  when  $S_{La}$  is turned OFF and a new switching cycle begins.

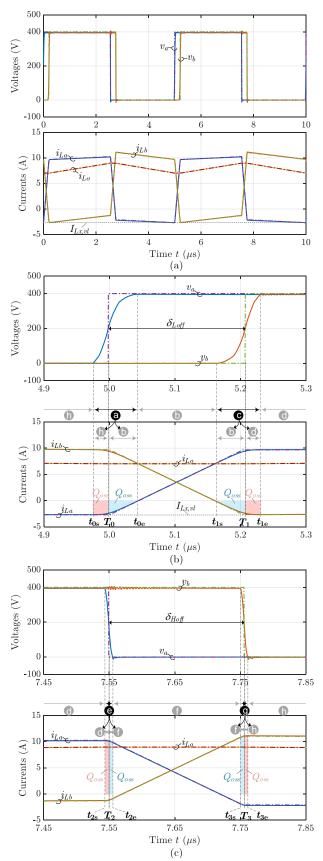

Fig. 6. Waveforms of switch-node voltages and inductor currents with the SPICE simulation (solid lines) and the linear MOSFET model (dashed lines). (a) Over two switching cycles. (b) Zoomed-in waveforms from stage (b) to stage (c) Zoomed-in waveforms from stage (c) to stage (c). (c) Zoomed-in waveforms from stage (c) to stage (c). The switching frequency  $f_s = 200 \text{ kHz}$ ,  $V_{dc} = 400 \text{ V}$ , D = 0.5,  $I_{Lo} = 8 \text{ A}$ , and  $S_{Ha}$ - $S_{Lb}$  are implemented with GS66508B GaN HEMTs.

IEEE TRANSACTIONS ON POWER ELECTRONICS REGULAR PAPER

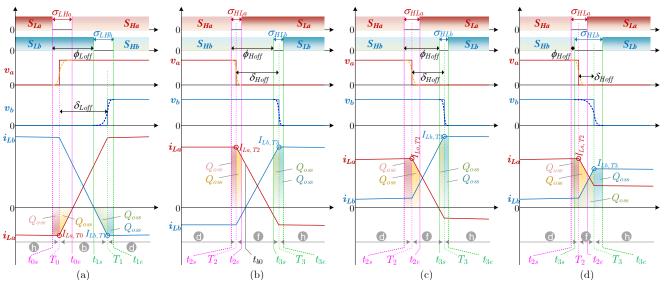

Fig. 7. Commutation modes under different conditions. (a) Commutation at  $t = T_0$  and  $t = T_1$ ; (b) Commutation at  $t = T_2$  and  $t = T_3$  when  $I_{Lb,T2} < 0$ ; (c) Commutation at  $t = T_2$  and  $t = T_3$  when  $I_{Lb,T2} \ge 0$  and  $t_{3s} \ge T_2$ ; (d) Commutation at  $t = T_2$  and  $t = T_3$  when  $I_{Lb,T2} \ge 0$  and  $t_{3s} < T_2$ .

TABLE I

Determination of the Time Delays and Deadtimes of Gate Signals

|                | Interval $[t_{0s}, t_{1e}]$<br>(See Fig. 7(a)) |                | $\begin{tabular}{c c c c c c } \hline Interval $[t_{2s},t_{3e}]$\\\hline $I_{Lb,T2} < 0$ & $I_{Lb,T2} \ge 0$ \\ \hline \end{tabular}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|----------------|------------------------------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                | (See Fig. 7(a))                                |                | (See Fig. 7(b)) $\phi_{Hoff} \ge \frac{Q_{oss}}{I_{La,T2}}$ (See Fig. 7(c)) $\phi_{Hoff} < \frac{Q_{oss}}{I_{La,T2}}$ (See Fig. 7(d))                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| $\phi_{Loff}$  | $\delta_{Loff} - \frac{Q_{oss}}{-I_{Lx,vl}}$   | $\phi_{Hoff}$  | $\left  \frac{Q_{oss}}{I_{La,T2}} - \frac{2I_{Lb,T2}L_c}{V_{dc}} + \sqrt{\left(\frac{2I_{Lb,T2}L_c}{V_{dc}} + \delta_{Hoff}\right)^2 - \frac{4Q_{oss}L_c}{V_{dc}}} \right  \delta_{Hoff} + \frac{Q_{oss}}{I_{La,T2}} - \frac{Q_{oss}}{I_{Lb,T2}} + \frac{\delta_{Hoff}^2 V_{dc}}{4L_c I_{Lb,T2}} \right  \delta_{Hoff} + \frac{Q_{oss}}{I_{La,T2}} - \frac{Q_{oss}}{I_{Lb,T2}} + \frac{\delta_{Hoff}^2 V_{dc}}{4L_c I_{Lb,T2}} = \frac{\delta_{Hoff}^2 V_{dc}}{V_{dc}} + \frac{\delta_{Hoff}^2 V_{dc}}{V_{dc}} + \frac{\delta_{Hoff}^2 V_{dc}}{V_{dc}} = \frac{\delta_{Hoff}^2 V_{dc}}{V_{dc}} + \frac{\delta_{Hoff}^2 V_{dc}}{V_{dc}} + \frac{\delta_{Hoff}^2 V_{dc}}{V_{dc}} + \frac{\delta_{Hoff}^2 V_{dc}}{V_{dc}} = \frac{\delta_{Hoff}^2 V_{dc}}{V_{dc}} + \frac{\delta_{Hoff}^2 V_{dc}}{V_{dc}} + \frac{\delta_{Hoff}^2 V_{dc}}{V_{dc}} + \frac{\delta_{Hoff}^2 V_{dc}}{V_{dc}} = \frac{\delta_{Hoff}^2 V_{dc}}{V_{dc}} + \frac{\delta_{Hoff}^2 V_$ |  |  |  |

| $\sigma_{LHa}$ | $\frac{3Q_{oss}}{-I_{Lx,vl}}$                  | $\sigma_{HLa}$ | $\frac{Q_{oss}}{I_{La,T2}} + \frac{2L_c \left( I_{La,T2} - \sqrt{I_{La,T2}^2 - I_{Lx,vl}^2} \right)}{V_{dc}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| $\sigma_{LHb}$ |                                                | $\sigma_{HLb}$ | $\delta_{Hoff} - \phi_{Hoff} + \frac{Q_{oss}}{I_{La,T2}} + \frac{Q_{oss}}{I_{Lb,T3}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

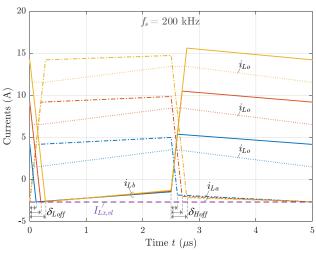

Fig. 8. Block diagram to determine the time delays and deadtimes of gate signals.

#### D. Simplification of Mathematical Model

The mathematical model above is nonlinear, and there are no closed-form solution for the two control variables, i.e., the two time delays  $\delta_{Loff}$  and  $\delta_{Hoff}$  between the two switchnode voltages  $v_a$  and  $v_b$ . These two time delays also represent the positive and negative pulse widths of DM voltage  $v_{ab}$ , as shown in Fig. 3. Therefore, in the first place, a linear MOSFET HB model [29], [40] is applied. With this linear model, the switch-node voltage of an HB leg jumps between 0 and  $V_{dc}$  with zero rise and fall time; the switch-node voltage remains unchanged until the parasitic output capacitances of the MOSFET HB are injected or ejected charge of  $Q_{oss}$ . A comparison between SPICE simulations and the results with the linear MOSFET HB model is shown in Fig. 6. Due to the high nonlinearity of the parasitic output capacitances of MOSFETs with respect to the switch-node voltage, the real inductor currents  $i_{La}$  and  $i_{Lb}$  during the resonant transitions are close to the case using the linear MOSFET model.

Applying the linear MOSFET model, each of the resonant stages, i.e., stages (a), (c), (e) and (g) can be split into two substages that further can be merged with its adjacent non-resonant stages, as shown in Fig. 6(b) and (c). With this linearization, only four non-resonant stages (b), (d), (f) and (h) remain within one switching cycle. The boundaries between these non-resonant stages are the four time instants  $T_0$ ,  $T_1$ ,  $T_2$  and  $T_3$ , as illustrated in Figs. 6(b) and (c). Also, it is seen that the currents  $i_{La}$  at  $T_0$  and  $i_{Lb}$  at  $T_1$  can be approximated by  $I_{La,t0s}$  and  $I_{La,t1e}$ , respectively.

$$\begin{cases} I_{La,T0} \approx I_{La,t0s} = I_{Lx,vl} \\ I_{Lb,T1} \approx I_{Lb,t1e} = I_{Lx,vl} \end{cases}$$

(27)

Thus, equations (16), (20), (23), and (26) for stages (b), (c), (f) and (b) are rewritten as (36)-(39) with modified initial conditions, as shown in the Appendix.

As aforementioned, the DM commutation inductance is relatively low (less than several  $\mu$ H), and thus, the two pulse widths of  $v_{dm}$ , i.e.,  $\delta_{Loff}$  and  $\delta_{Hoff}$ , are much shorter compared with the switching period  $T_s$ , which means that the presence of  $\delta_{Loff}$  and  $\delta_{Hoff}$  has a limited impact on the output current  $i_{Lo}$ . Therefore, initially it is assumed that  $\delta_{Loff} = \delta_{Hoff}$ . When the steady state is reached, we have

$$i_{Lo}(T_0 + T_s) = i_{Lo}(T_0) \Rightarrow I_{Lo,T_0 + T_s} = I_{Lo,T_0}$$

(28)

Fig. 9. Calculated (a) time delays and (b) deadtimes at different load currents and duty cycles.  $S_{Ha}$ - $S_{Lb}$  are implemented with GS66508B GaN HEMTs.

Substituting the steady-state condition 28 into (36)-(39) yields the load currents at  $t = T_0$  and  $t = T_1$ :

$$\begin{cases} I_{Lo,T0} = I_{Lo} - \frac{V_{dc}D[(1-D)T_s - \delta_{Loff}]}{2L_o} \\ I_{Lo,T1} = I_{Lo} - \frac{V_{dc}(1-D)(DT_s - \delta_{Loff})}{2L_o} \end{cases}$$

(29)

where  $I_{Lo}$  represents the average load current. Then, the initial commutation inductor currents at  $T_0$  and  $T_1$  can be obtained as

$$\begin{cases}

I_{La,T0} = I_{Lx,vl} \\

I_{Lb,T0} = I_{Lo,T0} - I_{Lx,vl} \\

I_{La,T1} = I_{Lo,T1} - I_{Lx,vl} \\

I_{Lb,T1} = I_{Lx,vl}

\end{cases}$$

(30)

Substituting (29) and (30) into (36) yields the closed-form expression for  $\delta_{Loff}$ :

$$\delta_{Loff} = \frac{2L_c \left[ 2L_o (I_{Lo} - 2I_{Lx,vl}) - (1 - D)DT_s V_{dc} \right]}{(2L_o - L_c)V_{dc}} \quad (31)$$

In the steady state, the commutation inductor currents at  $t = T_0 + T_s$  equals the initial currents, i.e.,

$$\begin{cases} I_{La,T0+Ts} = I_{La,T0} \\ I_{Lb,T0+Ts} = I_{Lb,T0} \end{cases}$$

(32)

Substitute (32) into (36)-(39), and we can obtain the expression for  $\delta_{Hoff}$  as

$$\delta_{Hoff} = \frac{2L_c I_{dm,T2}}{V_{dc}} + \frac{L_c}{R_{ds,on}} W_0(\frac{-2I_{dm,T0}R_{ds,on}}{V_{dc}} \times \exp[R_{ds,on}(\frac{(1-D)T_s}{L_c} - \frac{2I_{dm,T2}}{V_{dc}})])$$

(33)

where  $I_{dm,T0} = \frac{I_{La,T0} - I_{Lb,T0}}{2}$ ,  $I_{dm,T2} = \frac{I_{La,T2} - I_{Lb,T2}}{2}$ , and  $W_0$  is the 0th branch of the Lambert W function.

As seen from (31) and (33), the time delays  $\delta_{Loff}$  and  $\delta_{Hoff}$  vary with the load and duty cycle.

## E. Determination of Time Delays and Deadtimes of Gate Signals

The positive and negative pulse widths of the DM voltage  $v_{ab}$ , i.e.,  $\delta_{Loff}$  and  $\delta_{Hoff}$ , are determined by (31) and (33), respectively. For the high-side and low-side gate signals, their falling edges are delayed by  $\phi_{Hoff}$  and  $\phi_{Loff}$ , respectively. Due to the four deadtimes  $\sigma_{HLa}$ ,  $\sigma_{HLb}$ ,  $\sigma_{LHa}$  and  $\sigma_{LHb}$ , the time delays  $\phi_{Hoff}$  and  $\phi_{Loff}$  are not equal to  $\delta_{Hoff}$  and  $\delta_{Loff}$ , as illustrated in Fig. 3.

To determine the time delays and deadtimes of gate signals, the detailed commutation process within intervals  $[t_{0s}, t_{1e}]$  and  $[t_{2s}, t_{3e}]$  are shown in Fig. 7. The charge-based commutation model of power transistors [29], [41] is adopted to analyze the commutation time. The equations for time delays and deadtimes of gate signals are obtained and listed in Table I.

Fig. 8 shows the block diagram to determine the time delays and deadtimes of gate signals. In addition to the duty cycle D, the dc-bus voltage  $V_{dc}$  and the average load current  $I_{Lo}$ are required in (31) and (33) to calculate the theoretical time delays  $\delta_{Loff}$  and  $\delta_{Hoff}$  (i.e., the positive and negative pulse widths of  $v_{ab}$ ). After that, the derived  $\delta_{Loff}$  and  $\delta_{Hoff}$  are used to calculate the time delays and deadtimes of gate signals with Table I.

With the mathematical model above, the calculated time delays and deadtimes at different power levels are depicted in Fig. 9. It is seen that the two theoretical time delays  $\delta_{Hoff}$  and  $\delta_{Loff}$  have small differences with each other. The gate signal time delay  $\phi_{Hoff}$  is identical to  $\delta_{Hoff}$ , whereas  $\phi_{Loff}$  is shorter than  $\delta_{Loff}$  by  $\frac{Q_{oss}}{-I_{Lx,vl}}$ , as illustrated in Table I. For the four deadtimes,  $\sigma_{LHa}$  and  $\sigma_{LHb}$  are identical with each other and they are independent on the load, whereas  $\sigma_{HLa}$  and  $\sigma_{HLb}$  decrease with the increase of load.

## F. Simulation Verification of Mathematical Model

To verify the mathematical model developed in the preceding subsections, SPICE simulations of two QCM-paralleled GS66808B GaN HEMT HBs (configured as a synchronous Buck dc-dc converter) were performed with LTspice, as shown in Fig. 6. In the simulations, the time delays and deadtimes of gate signals are obtained from the equations in Table I. Under the same conditions, the linearized waveforms of the switch-node voltages and inductor currents obtained from the mathematical model developed in Subsections II-D and II-E are also shown in Fig. 6. It is seen that the linearized inductor currents coincide pretty well with the simulations, which verifies the accuracy of the above mathematical model in calculating the time delays and predicting the inductor currents.

## III. PERFORMANCE CHARACTERIZATION,

## IMPLEMENTATION CONSIDERATIONS AND COMPARISON

## A. Power Loss Characteristics of HB Legs

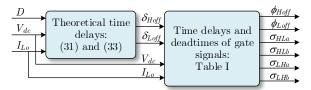

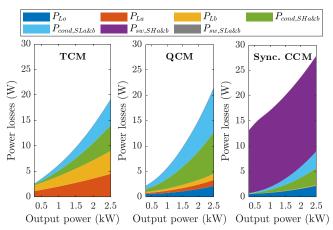

With the mathematical models above, we can generate the inductor and output current waveforms at different load currents, as shown in Fig. 10. In spite of the continuous conduction mode (CCM) output current  $i_{Lo}$ , the two commutation

IEEE TRANSACTIONS ON POWER ELECTRONICS REGULAR PAPER

Fig. 10. Inductor current waveforms at different loads and time delays. These waveforms are generated with the analytical expressions presented in Section II.

inductor currents  $i_{La}$  and  $i_{Lb}$  are reshaped as quadrilaterals. As the load rises, both  $\delta_{Loff}$  and  $\delta_{Hoff}$  increase, and thus, the peaks of  $i_{La}$  and  $i_{Lb}$  become higher. But the valleys of  $i_{La}$ and  $i_{Lb}$  remain negative at  $I_{Lx,vl}$  such that the two high-side transistors can achieve ZVS.

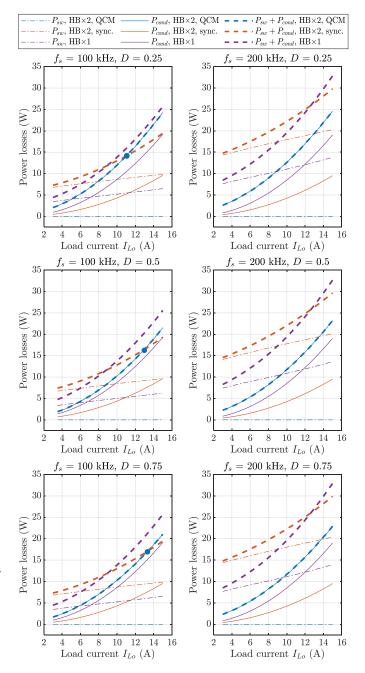

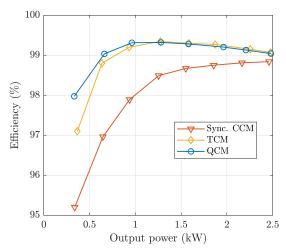

At different switching frequencies, duty cycles and load currents, the calculated power losses of two parallel GS66508B HEMT HBs operating in the conventional synchronous CCM and in the proposed QCM are shown in Fig. 11. The power loss characteristics of one HB leg operating in CCM is also shown in Fig. 11 for reference. Overall, the duty cycle has a limited impact on the power loss characteristics. Instead, it is the switching frequency and the load current that affect the power losses for the three schemes.

Compared with two parallel HB legs, the one HB legs has smaller switching loss due to the halved output capacitance of power transistors. Thus, at light loads, the non-parallel HB leg has lower power loss than the two parallel HB legs in CCM. As the load rises, the conduction loss increases and eventually the one HB leg generates higher power loss than the two parallel legs in CCM. Considering the transistor cooling surface area, the non-parallel structure suffers from even higher thermal stress than the two parallel legs.

With the proposed QCM scheme, ZVS can be achieved for all power transistors, and the switching loss can be significantly reduced. Thus, the QCM operation has the lowest power loss than the other two schemes. Nevertheless, the QCM operation increases the conduction loss. At low switching frequencies and high load currents (e.g., at  $f_s = 100$  kHz and  $I_{Lo} = 14$  A), the switching loss reduction is not as significant as the increase in conduction loss. Thus, the QCM operation generates higher total power loss than the two parallel HB legs in CCM. In this case, the operation mode of the two parallel HB legs should be switched from QCM to synchronous CCM. The DM inductor-based paralleling structure (see Fig. 1(b)) supports both the QCM and the synchronous CCM. This twomode compatibility enables the parallel HB legs to maintain low power losses from light to heavy loads.

Fig. 11. Comparison of power losses among three schemes: two HBs in QCM, two HBs in synchronous CCM, and one HB in CCM. Each switch is implemented with a GS66508B GaN HEMT and its switching loss characteristic is obtained by double-pulse tests (DPTs).

#### B. Effective Duty Cycle

It is seen from Fig. 3 that the duty cycle D in the QCM scheme should satisfy

$$\begin{cases} DT_s \ge \delta_{Loff} \\ (1-D)T_s \ge \delta_{Hoff} \end{cases} \Rightarrow \frac{\delta_{Loff}}{T_s} \le D \le 1 - \frac{\delta_{Hoff}}{T_s}$$

(34)

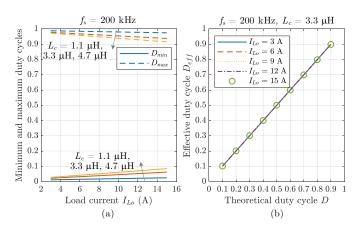

At a switching frequency of 200 kHz, the allowed minimum and maximum duty cycles at different load currents and DM inductances are shown in Fig. 12(a). As  $I_{Lo}$  and  $L_c$  increase, the two time delays  $\delta_{Loff}$  and  $\delta_{Hoff}$  rise, and accordingly, the duty cycle range becomes smaller. Overall, the duty cycle

IEEE TRANSACTIONS ON POWER ELECTRONICS REGULAR PAPER

Fig. 12. Duty cycle characteristics in QCM. (a) Duty cycle range allowed for QCM realization. (b) Effective duty cycle versus theoretical duty cycle at different load currents.

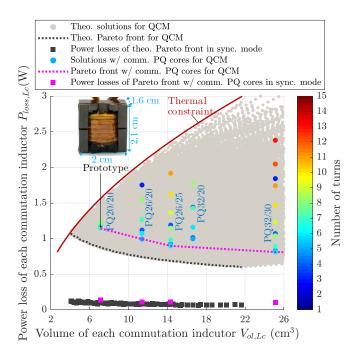

Fig. 13. Results of loss-volume Pareto optimization of the DM (commutation) inductors at the full load ( $P_o = 2.5 \text{ kW}$ ). The gray and black dots/squares/lines represent theoretical solutions. The colored dots/squares/lines are practical solutions with commercial standard PQ cores.

range for QCM is wide. For instance, at  $I_{Lo} = 12.5$  A and  $L_c = 3.3 \ \mu$ H, the duty cycle ranges are [0.05, 0.95] and [0.025, 0.975] for  $f_s = 200$  kHz and  $f_s = 100$  kHz, respectively. In the case of the duty cycle beyond the range, the operation mode can be switched to the synchronous CCM.

The pulse width of the common output voltage  $v_m$  represents the effective duty cycle  $D_{eff}$  of the parallel HB legs, as shown in Figs. 2 and 3. Within the duty cycle range, the effective duty cycle can be obtained as

$$D_{eff} = \frac{DT_s + \delta_{Hoff}/2 - \delta_{Loff}/2}{T_s} = D + \frac{\delta_{Hoff} - \delta_{Loff}}{2T_s}$$

(35)

As seen in Fig. 9, the difference between the two time delays  $\delta_{Loff}$  and  $\delta_{Hoff}$  is extraordinarily small (< 10 ns versus the

Fig. 14. Gate signal swapping between parallel legs for QCM operation. As the output current continues rising, the conduction loss may dominate the total power loss (depending on the switching frequency, see Fig. 11); in this scenario, the QCM can be switched to the synchronous mode to reduce the conduction loss and improve efficiency.

switching period 5000 ns). Therefore, the effective duty cycle is almost equal to the theoretical duty cycle, as illustrated in Fig. 12(b). It implies that the introduction of QCM has a negligible impact on the duty cycle control that is used to regulate the output voltage, current or power.

## C. Design Optimization of DM Inductors

1) DM Inductance  $L_c$ : As  $L_c$  increases, the absolute value of valley current  $I_{Lx,vl}$  becomes smaller, leading to lower RMS currents. On the other hand, a higher  $L_c$  brings a smaller duty cycle range (as shown in Fig. 12(a)) and a larger inductor size. Therefore, the selection of the DM inductance  $L_c$  involves multiple trade-offs regarding duty cycle range, power loss and volume. In this work,  $L_c = 3.3\mu$ H is chosen; the resulting duty cycle range and valley inductor current are [0.05, 0.95] (at  $I_{Lo} = 12.5$  A) and -2.73 A, respectively.

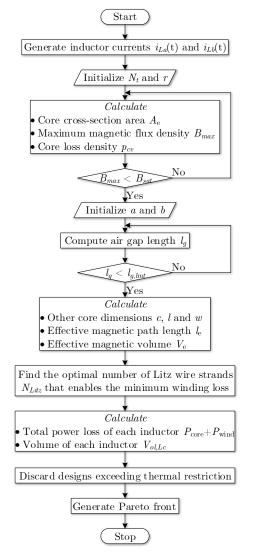

2) Loss-Volume Pareto Optimization of DM Inductors: In spite of the low inductance, the DM (commutation) inductors suffer from high current ripples, particularly at high load currents, as shown in Fig. 10. Thus, the DM inductors are prone to high fluctuations of magnetic flux density and high AC RMS currents. Accordingly, the core and winding losses or the inductor size can be significant without design optimization. Taking into account two objectives, i.e., power loss and volume, design optimization is conducted for the DM inductors implemented in the proposed QCM scheme. The details, e.g., the definitions of PQ magnetic core dimensions, the fixed and variable design parameters, and the flowchart of design optimization, are shown in the Appendix.

The design optimization point is chosen at the full load, i.e.,  $P_o = 2.5$  kW. The design results are shown in Fig. 13 where the black and purple dotted lines represent the theoretical and practical Pareto fronts, respectively. As can be seen, the Paretooptimal power loss decreases with the increase of inductor volume. With custom PQ cores, the power loss of each commutation inductor can be lowered to 0.6 W at an inductor size  $V_{ol,Lc} = 21.6$  cm<sup>3</sup>. With standard PQ cores, however, the inductor power loss is increased by approximately 0.25 W. Nevertheless, the power losses of the two DM inductors

#### TABLE II

COMPARISON AMONG DIFFERENT PARALLELING AND INTERLEAVING TECHNIQUES: THE QCM-ENABLED PARALLELING, THE CCM INTERLEAVING AND THE TCM INTERLEAVING. FOR A FAIR COMPARISON, THE THREE SCHEMES SHARE THE SAME SPECIFICATIONS, AS LISTED IN SUBSECTION III-E.

| Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | QCM-Enabled Paralleling                                                                                                                                                                                                                                                 | CCM interleaving                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | TCM Interleaving                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $V_{dc}$                                                                                                                                                                                                                                                                | $V_{dc}$ $V_{dc}$ $S_{La}$ $V_{dc}$ $S_{La}$ $V_{dc}$ $S_{La}$ $S_{Lb}$ $V_{dc}$ $V$ | $V_{dc}$ $S_{La}$ $V_{dc}$ $S_{La}$ $S_{Lb}$ $L_{a}$ $L_{a}$ $L_{a}$ $L_{a}$ $V_{b}$ $L_{b}$ $L_{b}$ $C_{a}$ $R_{a}$ $V_{a}$                            |

| Switching frequency $f_s$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Fixed or variable                                                                                                                                                                                                                                                       | Fixed or variable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Variable<br>High switching frequencies<br>at light loads                                                                                                |

| Output current ripple frequency $f_{iLo}$<br>Time delays between HB legs                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $f_{iLo} = f_s$<br>Less dependent on $f_s$<br>$\delta = - \operatorname{end} \delta = - i (31) (32)$                                                                                                                                                                    | $\begin{array}{l} f_{iLo} = 2f_s \\ \text{Directly dependent on } f_s \\ 1 \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $f_{iLo} = 2f_s$<br>Directly dependent on $f_s$                                                                                                         |

| ZVS inductors $L_a$ and $L_b$<br>Max. current in each ZVS inductor<br>Max. energy stored in $L_a$ and $L_b$<br>Output inductor $L_o$<br>Max. current in each output inductor<br>Max. energy stored in output inductors<br>Total energy stored in ZVS<br>and output inductors<br>Worst peak-to-peak current ripple<br>in output inductors<br>Required min. output capacitance $C_o$<br>to meet the output voltage ripple<br>requirement ( $\Delta V_{o,pp} \leq 0.5\% V_o$ ) <sup>d</sup><br>Max. energy stored in output capacitor | $\frac{\delta_{Loff} \text{ and } \delta_{Hoff}: (31), (33)}{3.3 \ \mu\text{H} \times 2}$ 15.6 A<br>0.8 mJ<br>119 \ \mu\text{H}^{b)}<br>14.38 A<br>12.3 mJ<br>13.1 mJ<br>3.75 A, 200 kHz<br>at $I_{Lo} = 12.5$ A<br>and $D = 0.5$<br>5.25 \ \mu\frac{F}{2}}<br>236.6 mJ | $\frac{1}{2f_s}$ N/A N/A N/A N/A 134 $\mu$ H × 2 <sup>c)</sup> 9.98 A 13.35 mJ 13.35 mJ 3.75 A, 200 kHz at $I_{Lo}$ = 12.5 A and $D$ = 0.25 or 0.75 5.25 $\mu$ F 236.6 mJ No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $\frac{1}{2f_s}$ 53 µH × 2 <sup>a)</sup> 13.32 A 9.23 mJ N/A N/A N/A 9.23 mJ 9.43 A, 200 kHz at $I_{Lo}$ = 12.5 A and $D$ = 0.25 or 0.75 16.3 µF 735 mJ |

| ZVS for all MOSFETs<br>RMS current stress of MOSFETs<br>Enable CCM to reduce conduction loss<br>Application suitability                                                                                                                                                                                                                                                                                                                                                                                                            | Yes<br>High<br>Yes<br>High<br>The output inductor and capacitor are                                                                                                                                                                                                     | No<br>ZVS only for low-side MOSFETS<br>Low<br>N/A<br>Low<br>The large output inductors are not                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Yes<br>Medium<br>No<br>Low<br>The large ZVS inductors are not                                                                                           |